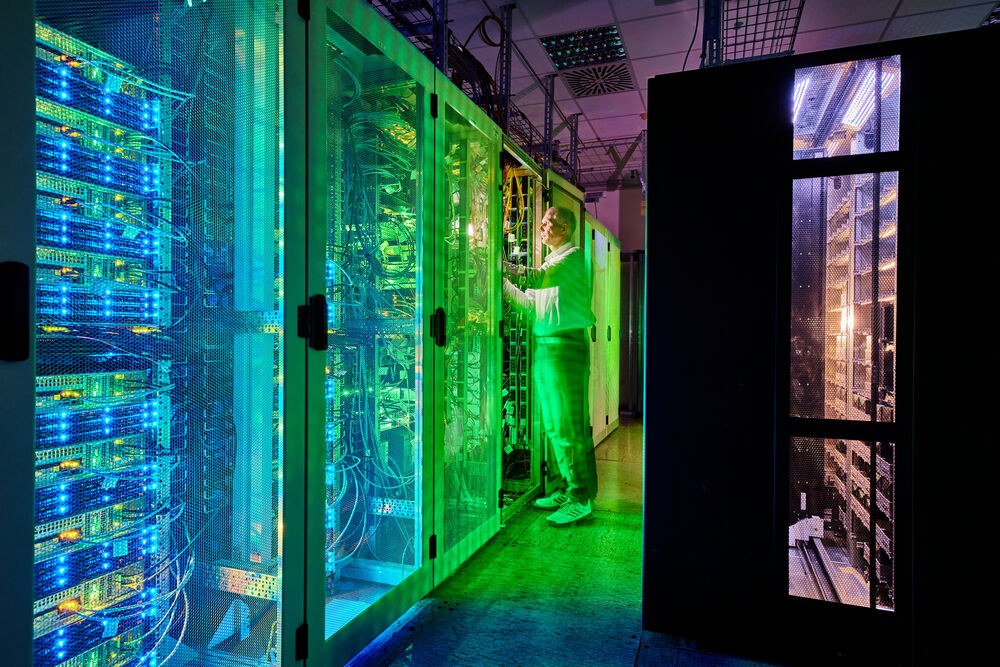

HPC Systems at the University of Bonn

The University of Bonn's largest system, Marvin, is operational since March 11, 2024. It is a significant upgrade compared to the previous small-scale computing systems, Bonna and Bender. Marvin consists of both MPP and GPU partitions, making it at least ten times larger than the combined capacity of Bonna, a Massively Parallel Processing (MPP) cluster and Bender, a Graphics Processing Unit (GPU) cluster. The implementation of Marvin represents a major advancement in the University's high-performance computing capabilities.

Have you used one of our systems, or our consulting services, for a publication? Remember to report and acknowledge it.

Available since March 11, 2024: Marvin – State of the Art Tier 3 Cluster

A much bigger HPC system, both with large MPP, as well as two extensive GPU partitions. Marvin is now available for users of the University of Bonn and collaborating partners.

Bonna – MPP Cluster

The cluster Bonna was purchased and installed in 2019 to meet small-scale needs for HPC resources. Bonna is a pure MPP cluster with 2240 cores. It is currently maintained by Fraunhofer SCAI.

Bender – GPU Cluster

For teaching and small research projects (e.g. a bachelor or master thesis) the University of Bonn offers the small GPU cluster Bender, consisting of 16 Nvidia A40 GPUs. Bender is currently open to all members of the University of Bonn. An application form can be found in the system description.

Research Data Management

The University and State Library Bonn (Universitäts- und Landesbibliothek Bonn, ULB) and the University Computer Centre (Hochschulrechenzentrum, HRZ) offer a common and central service for professional research data management.

HPC Projects

In addition to productive HPC ressources, the HPC team works on smaller playful yet educational projects. At this point in time, we offer students and trainees to build themselves a tiny HPC cluster, consisting of Raspberry Pis. Similar projects will be planned in the future.

HAL – Raspberry Pi Cluster

A tiny cluster continously re-assembled within the context of our workshops to demonstrate the basics of an HPC cluster's architecture.